**BMS**

INSTITUTE OF TECHNOLOGY AND MANAGEMENT

Avalahalli, Doddaballapur Main Road, Bengaluru – 560064

**DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

## DIGITAL SYSTEM DESIGN 18EC34

### **STUDY MATERIAL**

## **III SEMESTER**

#### **BMS** INSTITUTE OF TECHNOLOGY AND MANAGEMENT YELAHANKA – BANGALORE - 64

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

#### **COURSE DESIGN SHEET**

| Semester: IVECE | Course: DIGITAL SYSTEM DESIGN      | Subject Code: 18EC34          |

|-----------------|------------------------------------|-------------------------------|

| Academic Year:  | Course coordinator: HVR            | SIE Marks:40                  |

| 2020-21 Odd Sem | Course handled by: Dr.CSM,HVR, AGH | CIE Marks:60                  |

|                 | No. of Lecture hours /week: 4      | Total no. of Lecture:40 hours |

#### **COURSE OUTCOMES :**

| CO1                                                    | Apply the knowledge of simplification technique to solve digital logic circuits |

|--------------------------------------------------------|---------------------------------------------------------------------------------|

| CO2                                                    | Analyze and Solve circuits based upon digital logic.                            |

| CO3 Design simple applications using digital circuits. |                                                                                 |

#### **CO-PO-PSO Matrix:**

|     | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | <b>PO10</b> | <b>PO11</b> | <b>PO12</b> | PSO1 | PSO2 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------------|-------------|-------------|------|------|

| CO1 | 3   |     |     |     |     |     |     |     |     |             |             |             | 2    |      |

| CO2 |     | 3   |     |     |     |     |     |     |     |             |             |             | 2    |      |

| CO3 |     |     | 3   |     |     |     |     |     |     |             |             |             | 2    |      |

| Cii | 3   | 3   | 3   |     |     |     |     |     |     |             |             |             | 2    |      |

#### **JUSTIFICATION FOR CO-PO MAPPING:**

**CO1:** The Knowledge of Boolean Algebra is required to simplify digital circuits, hence the correlation of CO1 to PO1 is high.

**CO2:** Students should analyze and solve for the output in combinational and sequential circuits, hence the correlation of CO2 to PO2 is high.

**CO3:** Students should design simple applications/system using digital circuits, hence the correlation of CO3 to PO3 is high.

#### ASSESSMENT METHODS/TOOLS

| MODULES                 | DELIVERY<br>METHOD | ASSESMNENT<br>METHOD | CO<br>ATTAINMENT | EVALUATION<br>TOOLS |

|-------------------------|--------------------|----------------------|------------------|---------------------|

| Principles of           | Online Class-      | DIRECT-              | COl              | I-INTERNAL TEST     |

| combinational           | PPTs and           | INTERNAL TEST        |                  | PAPER               |

| logic                   | Videos             |                      |                  |                     |

| Analysis and            | Online Class-      | DIRECT-              | CO1,2            | I-INTERNAL TEST     |

| design of               | PPTs and           | INTERNAL TEST        |                  | PAPER               |

| combinational           | Demonstration      |                      |                  |                     |

| logic                   | of circuits        |                      |                  |                     |

|                         | using              |                      |                  |                     |

|                         | MULTISIM           |                      |                  |                     |

| Flip-Flops and its      | Online Class-      | DIRECT-              | CO1,2            | II-INTERNAL         |

| Applications            | PPTs and           | INTERNAL TEST        |                  | TEST PAPER          |

|                         | Videos             |                      |                  |                     |

| Sequential Circuit      | LECTURE            | DIRECT-              | CO1,2,3          | III -INTERNAL       |

| Design                  | CLASS              | INTERNALS            |                  | TEST PAPER          |

|                         |                    |                      |                  |                     |

| Applications of         | LECTURE            | DIRECT-              | CO1,2,3          | III-INTERNAL        |

| <b>Digital Circuits</b> | CLASS              | INTERNALS            |                  | TEST PAPER          |

|                         |                    |                      |                  |                     |

| SL.NO | Tools                | ASSESSMENT<br>Marks | COS MAPPED |

|-------|----------------------|---------------------|------------|

| 1     | Assignment-Module3&5 | 5 Marks             | CO2,3      |

| 2     | Quiz-Module1,2,4     | 5 Marks             | CO1,2,3    |

| 3     | Internal Assessment  | 30 Marks            | CO1,2,3    |

#### CO TARGET AND ATTAINMENT FOR PREVIOUS ACADEMIC YEAR AND **ACTION PLAN FOR THIS ACADEMIC YEAR**

|     | Target | Attainment | Action Plan                                                                                                                                          |

|-----|--------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| CO1 | 2.1    | 1.8        | <ul> <li>More Problems to be solved to make the students to analyse the problem</li> <li>More Assignments on Design problems</li> </ul>              |

| CO2 | 2.1    | 1.8        | <ul> <li>to be given</li> <li>Frequently asked questions of previous year QPs to be solved to make the slow learners to clear the subject</li> </ul> |

| CO3 | 2.1    | 1.8        |                                                                                                                                                      |

COURSE CO-ORDINATOR PROGRAM CO-ORDINATOR

HOD

#### **CONTENT SHEET**

| Module No | Name of the                 | Page No |

|-----------|-----------------------------|---------|

|           | Module                      |         |

| 1         | Principles of Combinational | 1-89    |

|           | Logic                       |         |

| 2         | Analysis and Design of      | 90-189  |

|           | Combinational Logic         |         |

| 3         | Flip Flops and its          | 190-223 |

|           | applications                |         |

| 4         | Sequential Circuit Design   | 224-242 |

| 5         | Applications of Digital     | 243-328 |

|           | Circuit                     |         |

DIGITAL ELECTRONICS 1.1 MODULE 1: PRINCIPLES OF COMBINATION LOUSE · Definition of combinational logic · lanomical forme Generation of sneitching equations from Tenthlables. Kaamangh Maps (3,485 Valiables) . Incompletely specified functions . Simplifying Maxteon equations Quine Mcclustey minimization technique. Quine Mcchekery using dont care terme. Reduced Perime implicants Taldes. Loge allering that contain no making . La reite TIL ECE

DEFINITION OF COMBINATIONAL LOGIC.

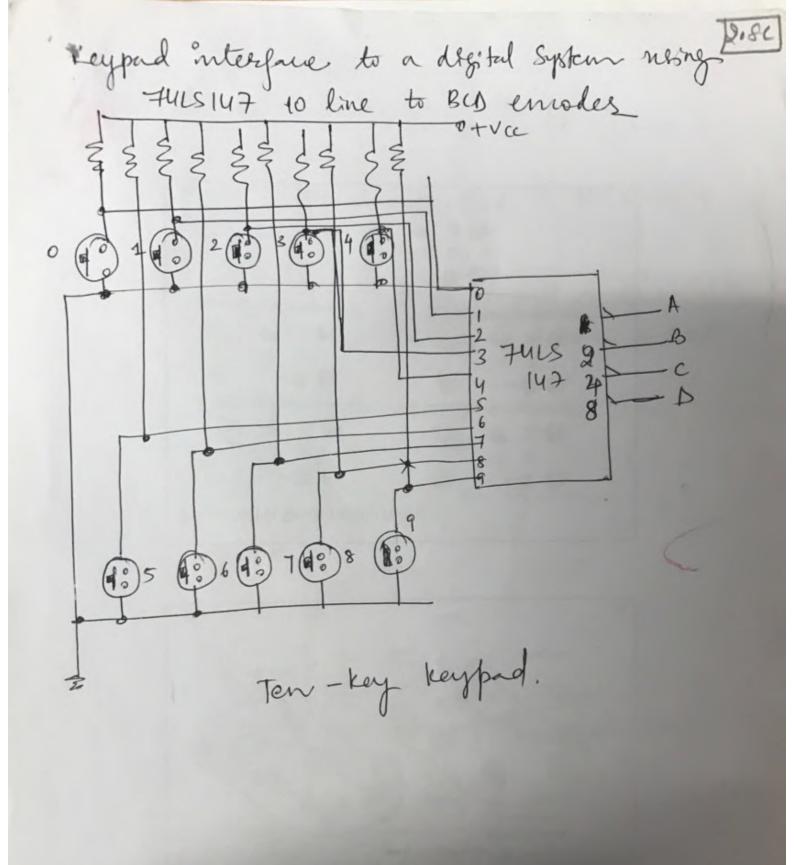

combinational logic deals with the techniques of combining the basic gates into circuits that perform some desired function. Ex: Addeus, Subtractore, Decoders, Emodere, Multiplieus, Divideus, Display drivers and Keyboard Encoders 35

Loyic circuit without feedback from output to the input, constructed from a functionally complete yate set, are said to be combinational.

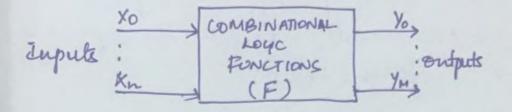

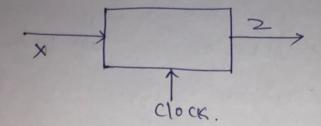

- Loyic circuite that contain no memory are combinational. COMBINATIONAL LOGIC MODEL.

Fig 1.1 - COMBINATIONAL LOGIC MODEL

- Let X be the Set of all input valiables E no, x, ... xn & and Y be the set of all -output Variables Stort, .... Ym} The combinational function <u>F</u>, operates On the input variable set X, to produce the output variable set Y.

Output Variables Yo through Ym are not fed chack to the Enput. The output is delated to Enput as

1.2

The Julationship between the input and output variables can be expressed in equations, logic diagrame or touthtables. - A teurth table specifier the input conditions under which the ops are thue or false (1020). - Sneitching equations are then denired from the touth tables and realized using gates. PROBLEM STATEMENTS TO TRUTH TABLE Before any combinational logic system can be designed it must be defined. Peroper statement of a problem is the most impostant pært of any digital delign task. Once concertly and clearly stated, any problem can be converted to the necessary logic for implementation.

1.3 GENERAL LOGIC DESIGN SEQUENCE Fig 1.2 illustorates the sequence of design tasks in a general way. Phoblem > Truth table Switching + Equations Statement Weitten 3 Built 6 Dearon 5 Equations Fig 1.2 . GENERAL LOGIC DESIGN SEQUENCE 1. First task is to define the Peroblem to ube solved. 2. The problem is then reversitten in the form of a territh table. 3,4,5. From the tenth latte, the Sweitching cquations can be weitten and simplified and the logic diagram drawn. 6. The logic diagram can be realized using any of the three main digital integrated circuit families.

TTL - Transistor - Transistor Logic, ECL - Emitter coupled logic or CMOS - complementary Metal-oxide Silicon.

Plaitical applications reaching come in a preparkaged teuthlable, heady for logic design.

Truthtables must be constructed from verbal problem desceriptions.

Ex 19 6, 7, 8, 91. Sint

. DERIVING SWITCHING EQUATIONS.

Boolean Equations can be directly derived from a touth take of from the logic bragram.

- Likeneise a touthtake of logic diagram Can be constructed from the Bodean Equations.

- Each input variable group that produces a logical 1 in a truthtable output column can form a term in a Boolean Switching equation.

For Example, in the following touth latte, the output variable M2 is a 1 in four cases.

S3 S2 S1 M4 M3 M2 M1 0 0 0 0 0 0 0 001100 1 0 1 0 1 0 1 0 0 1 1 1 0 0 1 1001100 1011001 1101110 1001 111

253', 52', 5, 3 , S, 52, 5, 9, 8, 9 , 853, 52, 5, 3 and 353,52, 519.

- The remaining input variable combinations cause output M, tobe a logical O.

- A boolean equation can be werttenthat defines all the conditione under which output M, is a logical 1.

- Each term in the equation is formed by ANDing the input variables. Each AND term is then ORed with the other AND terms to complete the output Boolean equation.

- For M, , the boolean equation would be written as

$M_{1} = S_{3}' S_{2}' S_{1} + S_{3}' S_{2} S_{1} + S_{3} S_{2}' S_{1} + S_{3} S_{2} S_{1} + S_{3} S_{2} S_{1}$

Each AND texan (Puoduct texa). identifies one input condition where. the output is a 1.

DEFINITIONS

". <u>LITERAL</u>: A Literal is a Boolean Variable Or its complement. Ros instance, let X be a binary variable, then both X and X' would be literals.

AND THE TOTAL

- ·2. <u>PRODUCT TERM</u>: A Peroduct term is a literal Or the logical product (AND) of multiple literals.

- Pos instance, let X, Y and Z be the binary Variables. Then a representative product term could be X, XY, XYZ or X'YZ etc.... .3. <u>SOM TERM</u>: A sum is a literal or the logical OR of multiple literals. Let X,Y and Z be the binary variables. Then a representative sum term could be X, X'+Y, or X+Y'+z' etc...

- .4. <u>Sum of PRODUCTS</u>: A sum of Products (SOP) is the logical or of multiple product terms. Each product term is the AND of binary biterals. For ex: XY' + X'+YZ + XY'z' is a SOP Expression.

:5. PRODUCT OF SUMS: A Product of SOMS (Pos) is the logical AND of multiple or terms Each sum term is the or of binary. litelials. For ex: (X+y')(x+y+z')(y'+z') is a Pos expression. = 6. MANTERM: A Minterm is a special case product (AND) term. A mintern is a product, that contains all of the input Variables (each literal no more than once) that make up a boolean expression .T. MAXTERM: A maxtern is a special case SUM (OR) term. A maxtern is a Sum term that contains all of the input variable ( each literal no more than once) that make up a boolean cupression. -8. CANONICAL SUM OF PRODUCTS: A conomical sum of products is a complete set of minterine that defines when an

output variable le a logical 1.

Scanned with CamScanner<sup>10</sup>

Each minteum colleceponde to the none in the teuthlathe where the output function is 1 i.e., the SOP for the output M in the following table is M = a'bms + ab'ms + abms.

bm a S M 0 1 0 A 0 1 - à bms abms OIK Ð 0 abms 9. CANONICAL PRODUCT OF SUMS: A canonical product of sums is a complete set of maxteerne that defines when an output is a logical O.

Each maxtesum covresponds to a now in the tenthtable where the output is a D

#### Scanned with CamScanner<sup>11</sup>

1.9

i.e., the pos for the output Os in the following table is  $O_1 = (1 + (2 + (3))(c_1' + (2 + (3))(c_1' + (2 + (3)))(c_1' + (2 + (3 + (3)))(c_1' + (2 + (3)))(c_1' + (3 + (3)))(c_1$ \* (C'+C'+C')

- (G+G+3) 9 2 3 01 00000c0011c (c1+2+3) 000 010 1 (4+52+53)  $1 \leftarrow (G_{1} + G_{3} + G_{3}) + (G_{1} + G_{2} + G_{3})$ 011 0 E (C1+Ca+C3') (100 (101 0  $(c_{1}+c_{2}+c_{3})$ (110 0) (G1+5'+5') 111

The table 1.1 Shows the complete nature of minterins and maxterins.

- In Enpit valiable is completaenlet when it has value of the are writin minterine.

- The Engent vaeuables ale complemented when they have a value 1, if we are writing masterine.

#### Scanned with CamScanner<sup>12</sup>

- Minterine represent output vaenable Is and masterins fignerent output Vaenables OS.

dower care m is used to denote a mintern and Upper care M is used to denote a maxtern.

The number subsceript indicates the derival value of the term.

| aba | MINT   | MINTERM     |           | AXTERM      |

|-----|--------|-------------|-----------|-------------|

| abc | TERM   | DESIGNATION | TERM      | DESIGNATION |

| 000 | a'b'c' | mo          | (a+b+c)   | Mo          |

| 001 | abc    | ma          | (atbtc')  | Mi          |

| 010 | abc    | mz          | (a+5'+c)  |             |

| 011 | a'bc   | mz          |           | M2          |

| 100 | abici  | my          | (a+b+c)   | M3          |

| 101 | ab'c   | mo          | (a+b+c)   | > M4        |

| 110 | abc    | mb          | (a'+5'+c) | MC          |

| 111 | abc    | mz          | (a+6+c)   | SMI         |

Table 1.1 - Mintern & Maxtesm Designations

- output equations can be directly from the touthtable using either minterne of maxtorms.

- when an output equation is weiten in minterine of maxterne, it is a canonical expression.

#### Scanned with CamScanner<sup>13</sup>

# CANONICAL FORMS

Canonical is a word used to describe a condition of a switching equation. In normal use the word means " conforming to a general sule". The Aule for Switching logic, is that lach term used in a suitching equation must contain all of the available input valiables. Two formate generally exist for expressing Switching equations en a Canonical form. () sum of Minteems (Produits) (2) Product of Maxterne. (sums) Canonical expressions are not simplified why canonical forms ????? 1. U Situations that occurs when logic designers must manipulate Boolean equations for proposes other than simplification. (2) conversion from one from to another form (TTL Nand Gales to ECL NOR Gales) (3) Entry into the Rasnaugh Map.

#### Scanned with CamScanner<sup>14</sup>

I. SOP Equation to Canonical form. To place a SOP equation to canonical form using Boolean algebra, we do the Gollowing (i) Edentify the missing variable (s) in each AND term. (xy) (ii) AND the missing term and it's complement with the durginal AND term. my (2+2) Because (Z+Z') = 1, the original AND term value is not changed. : - (iii) Expand the term by application of the property of distabilition ny(z+z') = nyz + nyz' · 2. Pos Equation to canonical form To place a los equation to canonical form using Boolean Algebra, ne dottis (i) Identify the missing variables in each OR term (x+y')

#### Scanned with CamScanner<sup>15</sup>

(ii) OR the missing teame and its complement neith the oniginal OR tesm.

Original : X+Y' Modified : (X+Y'+ZZ') & Oring missing > Because ZZ'=0, the original ferringement value is not changed.

(iii) Expand the team by application of distributive property.

(x+y'+zz') = (x+y'+z)(x+y'+z')

<u>CLENERATION OF SWITCHING EQUATIONS PROM</u> TRUTH TABLES

Sueitzhing equations can be weitten more conveniently by using the minteson or maxiterin numerical designation as shown in Table 1.1 (pg. NO 1.10), instead of whiting the variable names On their complements.

#### Scanned with CamScanner<sup>16</sup>

the team can be weather discertly. 1. CANONICAL SOP EQUATION for ep: consider the canonical SOP equation l'= abc + abc + abc + abc + abc

For decode each of the minternes based on trinary weighting of each variable and produce a list of decimal decoded minternes, the result would be

P= Z(5,4,6,7,3)

- To keep the input variable notation from being lost in a mintern flist the selationship P = f (a,b,c) is used.

This means that the output variable P is a function of the set of input variables {a, b, c } with input variable

a being the most significant bit (use).

The sign ∑ indicates Summation and stands for the sum of Peroducts canonical your

- when numbers in a definal decoded set are preceded by a Z sign, a

#### Scanned with CamScanner<sup>17</sup>

Sop expression is indicated. Each number represents a montesm. P = f(a,b,c) = (abbc + abbc' + abc' + abc + a'bc) $= \sum (\xi, 4, b, 7, 3)$

2. CANONICAL POS EQUATION.

- Canonical Pos expressions can be whitten in similar fashion as SOP expressions

- Tr (Pi) Sign 1s used to indicate Pos canonical form.

- The decimal number listed in a Pos set represents maxtesme.

- The Engut valiable names alle indicated in the same manner as in SOP equations. X = f(A, B, C)

- Maxterine are complement ef minterine. KARNAUGH MAPS.

- Simplification of Sneitching equations reduces the amount of hardware needed to realize a Given function.

- Reduction of gates and yate Enputs may result in fewer integrated irecuite, which in turn decreases cost and Emproves reliability.

- Boolean Algebra can be used to simplify equations but the process is lengthy and error prove.

- It is required a Systematic method for finding and eliminating any redunctions in an equation.

- A betten approach is the use of karnaugh map. The karnaugh map is a mataix of Squares. Each Square represents mintern & martenn from a boolean expression /equation. The arrangement of the mataix square permite Edentification of input variables redundancies, which helps reduce the output equation

Edentifies all of . - The Rosnangh map the cases for a given set of Engut variables where groups of menterine may contain redundant variables of the. when these groups form x+x'= I. the seduct variables are identified, Can be eliminated dissulting in a simplified output function. If a given Sneitching equation contains a monterien, then a 1 is entered, into the square that represents that term, A maxtern is supresented by a O. Two variable &- map. (MSB) (ALE O 1 0 12 Brinaly 2 2 Value 2 cimal value. All four possible combinations of Enput valuables are supresented.

#### Scanned with CamScanner<sup>20</sup>

THREE AND FOUR VARIABLE KARNAYH MAPS. - The fig deprecents three -valuable harnaugh map.  $(150) \xrightarrow{AB} \xrightarrow{O} OO OI 11 10 \\ 0 \xrightarrow{2} 6 4 \xrightarrow{4} Derinal value. \\ 1 \xrightarrow{1} 3 7 5 \xrightarrow{1} 5$

Each Squale in the map represente a possible mintern og maxtern of a 3- Valiable function.

- The upportent square représents traney 000, minteeur (14'B'c') or maxtern (14+B+c). - its three trinany valuables can représent eight (8) unique combinations, ve find 8 squares are needed.

- if minteun A'k'c' (000) occurred in a Sneitching equation, then a I would be Enserted into the upper left square.

- Assignment of a square to each of the 8 minteume tresulting prom 3- Euph variables tresults in given Table.

#### Scanned with CamScanner<sup>21</sup>

| Timb | linter | Maxtesm |  |

|------|--------|---------|--|

| ABC  | m      | M       |  |

| 000  | 0      | 0       |  |

| 001  | 1      | 1       |  |

| 010  | 2      | 2       |  |

| 011  | 3      | 3. 8    |  |

| 100  | 4      | 4       |  |

| 101  | 5      | 5.      |  |

| 110  | 6      | 6       |  |

| 111  | 7      | Ŧ       |  |

We may label the decimal value for each square in a kalnaugh map by decoding the bonany numbers as showen in fig ( ).

Accords the lop and down side of the 3 variable k-nap only one bit changes ocur between adjacent squares pe cach column and how Fach adjacent vous or column differs my only one valiable

#### Scanned with CamScanner<sup>22</sup>

FOUR VARIABLE K-MAP. is the same length both hosizontally and vertically Valiable représentation is the same in both directions, two variables access (00,01,10,11) and two down. The Enget valiable binany weighting is  $W = 2^{3} = 8, X = 2^{2} = 4, Y = 2^{2} = 2, Z = 2^{2} = 1$ (MSB) MSB, Z-> LSB. 1200001 11 10 E Binary ralnes for 121. 00 Derimal 01 5 13 9- Derimal Values Binary 7 15 11 6 14 10 PI 72.2 EPI 72.2 10 3 values for 10 2 fg(): four vacuable &- Map. Loading &- map involves weiting I in the Squares corresponding to a coursponding to a maxterin.

#### Scanned with CamScanner<sup>23</sup>

STEPS INVOLVED IN LOADING & DETERMINING THE ESSENTIAL PRIME EMPLICANTS.

Step 1: load the minterines into the 2-map. by placing a 1 in the appropriate Square.

- Slep 2: Look for Groups of minterime (P2) (a) Group size must be a power of 2 (° of Binary member system)

- (b) fis are formed from Groups of minterns whose size is a power of 2. Mintern Group Size that are not an integer power of 2 are not permitted. - End the lowert

- Find the largest groups of mintering first, then progreesively evaluate smaller collections of minterens until all yroups are found.

Step 3 Once all of the possible PIs have been identified, we determine whether any have minterens that. are unique. If so , that PI Esan Elsential Perime Emplicant (EPI)

Step 4 : Select all essential prême implicante and a minimal set of remaining Perime Emplicants that cover all lemaining Is in the K-Map.

Steps: Make than one equally Simplified desult is possible when make than one set of remaining Pss contain the same no. of mintering and maxterne.

Five VARIBLE K-MAP.

ABC

Five Vaerable &-maps can be constructed so that 3-vaerables are laid out hoerizontally and 2 vertically as shown.

ODD DE 161 100 IS H fg(): 5-variable &- Map.

A, B, C, D, E are the Enget variables. 25 possible combinations exist, langing: from (00000)2 to (1111)2  $A \in MSB$ 24 = 16 = 08 C 22 = 04 D 2' = 02 20 E LSB .= 01 The definal value accorrated with each Square in the map is found by adding the column and now values. Each half of the five - vaeiable map corresponds to a single 4-variable R-Map. STACKED VERSION OF 5-Variable K-MAP. ABC 110 010 DE 000 00 101 100 12 8 24 28 20 16 on 925 IVKA 29 13 21 5 17 64 01 UVKM 3 1 27 31 7 15 23 18 11 10/2 14 6 10 26 30 22 -1 18 Ku-valiable k-Map - K-4- herable K- Map.

#### Scanned with CamScanner<sup>26</sup>

### INCOMPLETELY SPECIFIED FUNCTIONS.

(DON'T CARE TERMS)

· when an ontput value is known for every possible combination of input valuables, the function is Said to be completely specified.

- when an op value is not known for every combination of input variables, usually because all combinations cannot occur, the function is said to be incompletely specified.

- The minterine of maxterine that are not used as a past of the output function are called don't care terms.

- For ex! Binary to Ex-3 BCD as shown in Table.

- BCD codes including Ex-3 can represent only a single digit decimal character (0 to 9)

- The definal number 9 lakes 4-bits in Ex-3 BCD code.

- Input combinations (10, 11, 12, 13, 14, 15) indecind are not used to specify any output variable

#### Scanned with CamScanner<sup>27</sup>

1.17

Value outputs A, B, C, D ale incompleteling specified for those Enput code values that are don't care teams.

Touth lable for Binany to Ex-3 BCD code conversion.

| Binaly | EX-3 BCD   |

|--------|------------|

| wxyz   | ABCD       |

| 0000   | 0011       |

| 0001   | 0100       |

| 0010   | 0101       |

| 0012   | 0110       |

| 0100   | 0 11 1     |

| 0101   | 1000       |

| 0110   | 1001       |

| 0111   | 1010       |

| 1000   | 1011       |

| 1001   | 1100       |

| 1010   | Don't call |

| 1011   | - u        |

| 1100   |            |

| 1101   |            |

| 1210   |            |

| 1411   | <u> </u>   |

| T++-   | 1          |

- Writing the equations for output variables A.B., CD, Encluding the don't care lows, We yet.

$$\begin{split} \mathcal{A} &= f(\omega, \varkappa, y, z) = \Xi(\xi, b, 7, 8, 9) + \Xi d(10, 11, 12, 13, 14, 15) \\ \mathcal{B} &= f(\omega, \varkappa, y, z) = \Xi(1, 2, 3, 4, 9) + \Xi d(10, 11, 12, 13, 14, 15) \\ \mathcal{L} &= f(\omega, \varkappa, y, z) = \Xi(0, 3, 4, 71, 8)' + \Xi d(10, 11, 12, 13, 14, 15) \\ \mathcal{D} &= f(\omega, \varkappa, y, z) = \Xi(0, 2, 4, 6, 8) + \Xi d(10, 11, 12, 13, 14, 15) \end{split}$$

Don't care terms are distinguished from regular minterine in that it doesnot matter whether we assign them a value of 0 or 1, because there input combinations never occur.

Don't care terms are indicated by a din each of the k-maps.

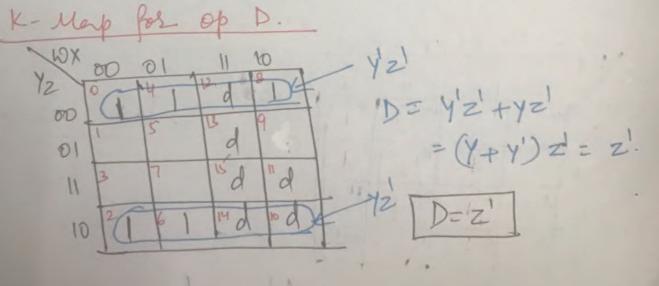

K-Map wop A XCJ 02 12 d 81 N 12 A = W+XZ+XY 10 00 13 d 191 ST - XZ 01 "1 HI Wa 11 10 d 10 > XY

#### Scanned with CamScanner<sup>29</sup>

K-Map for op B.

B = X Y z' + X' z + X' Y.

K-Map for op C.

#### Scanned with CamScanner<sup>30</sup>

Procedure for the determination and me of don't care terms. · Or Develop the territh take that descentes the Enget / output relationship. ②→ Determine if all of the input combinations are used to generate the ops. (a) if so, then no don't care teams exist. (6) if not, then those combinations of input variables not used to determine output values are don't care terms. (3→ once the don't calle telems have been identified, use a separate symbol, in the K-Map squares. Create as læge an EPI grouping as poliske, melnding don't care teems that have been couldsned with normal minteerns. (4) > B → Do not group don't case teems by themselves. A don't care l'é meaningless, because don't case terms are not used to generale the output function.

## Scanned with CamScanner<sup>31</sup>

- and while and a contract where I marting some as and and Bounded with the series and grander the athen the second will converted the the allegad - allegad ( 200 ( 200 ) C The stand have a radiency so all and mind all indicant prover a matches prevent New marges have " while you - Mindates and a sunt

QUINE - MC CLUSKEY MINIMIZATION TECHNIQUE.

For many applications, the no. of Variables in a problem is too large to simplify manually using k- maps. Simplification typically means that a logic designer can obtain more functional we from a given component. Therefore some automatic or computer deren Somplification montire is desierable. The QUINE - MCCLUSKEY miningation technique is an algoeithm that were the same boolean Algebra portulates that were used with Karnange Maps but in a form suitable for a computer solution. Large &- haps requile recognition of Group of texas that may form elsential prime implicante. The larges the map, the more difficult this pattern recognition becomes. The QM approach climenales the need for such pattern recognition.

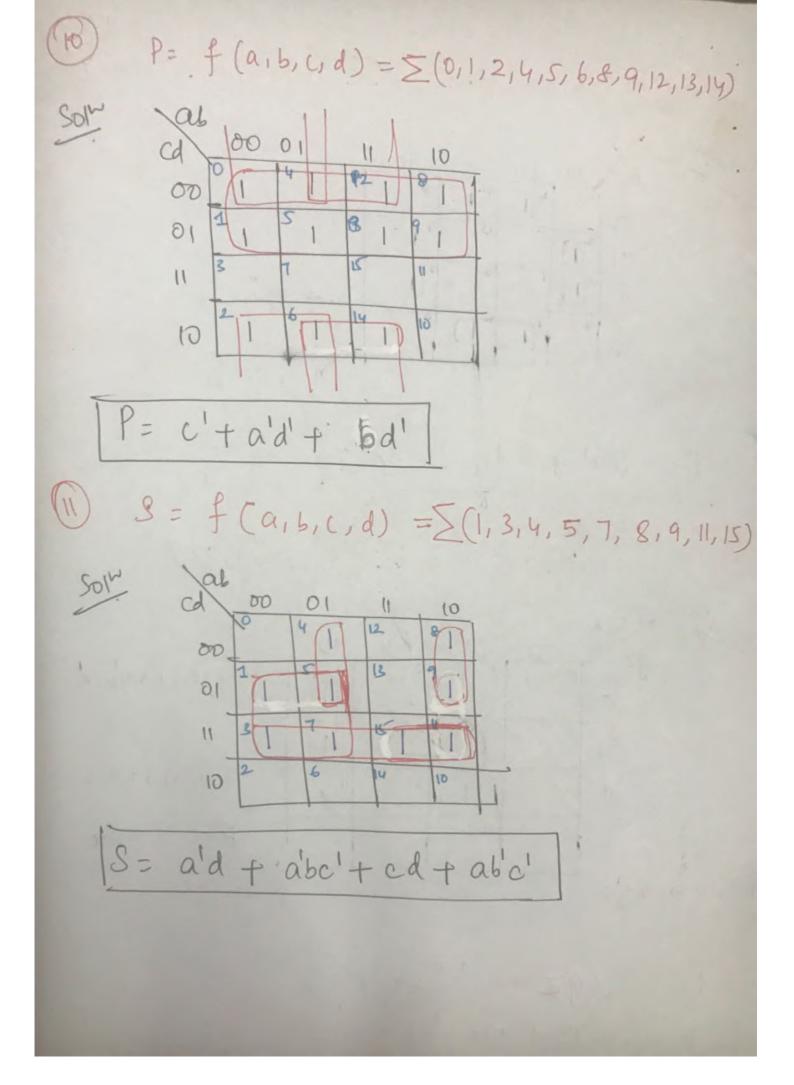

Ex: Simplify the following wing the an Minimization technique.  $D = f(a, b, c, d) = \Xi(0, 1, 2, 3, 6, 7, 8, 9, 14, 15).$ Case 1 Using K-Map. cd oo 14 - LEPI 12 80 be 15 9 13 01 151 11 TTT (a'b) PI-10 21.161 141 - EPI (bc) pt (a'c) D= bc+bc+ab 02 D= b'c'+bc+a'c. Cused : QM Technique. Steps: Allange all of the minteeme, En a list of increasing order, so that yroup of texas contain the same no. of 1s. - Each mintelim en the obiginal expression is arranged in increasing order according to ho, of 1's contained each yroup.

1.21 yeurp o contains no. 28., youp 1 contains only those mintering that have single 1 (1,2,8), yearp 2 contains minteens with two is (3,6,9), yroup3 Contains minterine with three is (7, 14) and yroup 4 contains ninterns neith forer 1's (15). & yroup I groups 0-> 0000, 1>0001, 2>0010 8 -> 1000 [3> 0011, 6>0110, 9>1001 ~ yeoup2 17+ 0111, 14+110 eyroup3 TIS > TIT < yroup 4. Grouping minterms according to no. of 20 Group Minterin abed 0000 1 1 0001 0010 2 1 8 1000 9 3 0011 6 0110 9 1001 3 7 14 1110 15 4 11 1 Table 1.

Step 2: create a new lable showing the monteerns in youp n (ex:0) that matched with those from Goup n+1 (1) such that they differ en only one position. - compare muterim 202 in group o of Take I with each of minterus in youp 1. when all the mintering in years a have been compared with those in Group 1. mintesmin Compare the Groups with those in yroup 2. This process is repeated until all of the minterins in each group have been compared to those of in the next higher group. when a minteum in a group combined with a minteen in adjacent youp, a dash (-) is used to indicate an eliminated valiable. The combined minterns are Grouped together in Table 2. Each combination desulte in a new mintelen group.

## Scanned with CamScanner<sup>36</sup>

Table 2: creation of minteren Groups of two.

| Group | Minteen | abcd      |

|-------|---------|-----------|

| 0     | 0,1     | 000       |

| 0     | 0,2     | 00-0-     |

| 0     | 0,8     | - 000 -   |

| 1     | 1,3     | 00-1-     |

|       | 1,9     | - 001     |

|       | 2,3     | 001       |

|       | 2,6     | 0-10      |

|       | 8,9     | 100       |

| 2     | 3,7     | 0_11.~    |

|       | 6,7     | 011       |

| _     | 6,14    | -1100     |

| 3     | 7, 15   | - 1 1 1 / |

|       | 14,15   | 111_/     |

|       |         | ,         |

As each minteeur, combines with a minteeur in the next higher Group's checked (1), indicating that it is now part of a larger group.

1.22

All of the adjacent montesion Step 3 groups contained in Table @ are compared to see if youpsof 4. can be made.

- The centeenia for forming Groups of 4 are as follows.

- (a) The dashes in the groups of two must be in the same bit position and (b) only one variable change is allowed.

- A comparison is made of early minterim in yroup n with early ninterim in yroup n+1. Those that neet the certerisa are combined in a larger group as shown in Table 3.

| youp | Minteem 1 | abcd |

|------|-----------|------|

| 0    | 0,1,2,3   | 00   |

| 0    | 0,1,8,9   | -00- |

| 1    | 2,6,3,7   | 0-1- |

| 2    | 6,7,14,15 | -11_ |

Table 3: breation of Minterens of group of 4.

## Scanned with CamScanner<sup>38</sup>

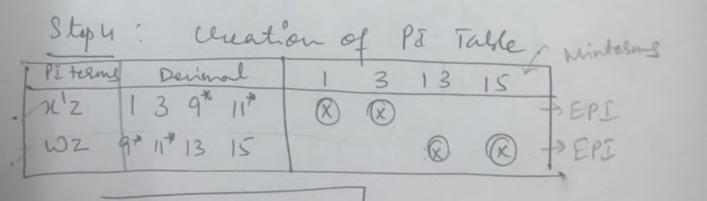

Steph: Minteens \$0,12 in yroup 0 is compared with \$2,33 in Group 1, to form a Group \$0, 1, 2, 34 position and only one Variable changes then a newer group is cleated. This proceed is superated until no further combination is politike. That is tach minteren in group n is compared with each minterim Group in n+1 in Table (). Step 5 + All nonchecked minter groups are now considered as PIs. slepb & All of the PIS are formed into a PI Table as Shonen in Table @ PItorne Decimal 1 2 36 7 8 9 14 15 0 a' 61 0,1,213 × × × × × × bel 0,1,8,9 a'c × × × × × × Ø® 2,6,3,7 Se 6,7,14,15 Table 4: Prime Implicant Table.

## Scanned with CamScanner<sup>39</sup>

- The prime Emplicant take lists each of the minterins contained in the Original Sweitching equation across the top of the table.

- Each PI is listed vertically in 2 forme. PI terms and the definal list of mintermis that make up the PI.

Step7 > Evenhalt the prime implicante by children those minterms that also contained in only one PI (only one X in a column).

- The minterener (8,9,14,15) meet this. condition -> Essential PI.

- (0,1,8,9) & {6,7,14,15} are EPI.

- Minteennes {2,3} ave contained in 2 PTs \$ 0,1,232 & \$2,3,6,72. We need one of the other of these PIs to cover minteeins in the equation but not both.

D= 6,6 +,6c+a'b' D = b'c' + bc' + a'c

## Scanned with CamScanner<sup>40</sup>

QUINE-MCCLUSKY USING DON'T CARE TERMS [1.24]

The same sucles that applied to using don't calle terms with the k-Map are appropriate for QM technique. Ex:  $S = f(w, x, y, z) = \sum_{i=1}^{n} (i, 3, 13, 15) + \sum_{i=1}^{n} (8, 9, 10, 11)$ Step 1 : Constant a list of minterens and don't care terms classified according to the number of 2s. Indicate the don't care telems by using a \* symbol. Don't care terms are never included as prime implicants by themselves. -> 0001 3-> 2011 15 -> 1111 13- 1101 8"> 1000 93 1001 11 → 1011 youp A 10-1100 yroup3 croupp youpt yroup wxyz Mintern 0001 87 1000 3 0011 2 q+ 1001 1100 100 11+ 10 1 1 3 13 1101 15 1111 4 Table 1 .: grouping of minterens.

## Scanned with CamScanner<sup>41</sup>

Step 2: compare terms in yearp n. including don't calle terms in group. n+1, for a single variable change. Treat don't care learns as a 1 m finding Pis.

| youp  | Minteam     | w xyz       | 1120 |

|-------|-------------|-------------|------|

| 1     | (1,3)       | 00-1-       |      |

| 1     | (1,9*)      | -001~       |      |

| 1     | (8,9*)      | 100         |      |

| 1     | (8, 10*)    | 10-0-       |      |

| 2     | (3,11+)     | 1011-       | -    |

| 2     | (g* 11*)    | 10-1-       |      |

| 2     | (9 + 13)    | 1-01-       |      |

| 22    | (o*, 11*)   | 101-2       | 1    |

| 3     | (11*,15)    | 1111        |      |

| 3     | (13, 15)    | 11-1-1-     |      |

|       | 1           |             | 1    |

| -     | 0 · 11' + 0 | 11 Glouble  | 1 l  |

| Table | 2. Mule     | en groups o | 4    |

|       |             |             |      |

|       |             |             |      |

|       |             |             |      |

Step 3: Repeat Stip 2 to create a latte of youp of 4 minteen and don't care teens. Repeat step 3 until no pulither grouping can occur.

| group | Minteren      | wxyz |

|-------|---------------|------|

| 1     | 1,3,9,11      | -0-1 |

| 1     | 8,9,10, 11,00 | 1.0  |

| 2     | 9,13,11,15    | 12-1 |

Table 3: Minterna groups of 4.

- Table 3 représenté group of 4 minterns and don't care terms. Each term is EPI. Bont (8\*,9\*,10\*, 11\*) contains only don't care terms : not a PI.

: S= WZ+ X'Z

-1. Place the following equation into proper canonical form. a) P = f(a, b, c) = ab' + ac' + bc (sop) Sol<sup>w</sup> P = ab'(c+c') + ac'(b+b') + bc(a+a')= ab'c. + abc' + abc' + abc + abc + abc P= abc +abc + abc -+ abc -+ abc -+ abc. b)  $G = f \left( \omega, \chi, y, z \right) = \omega' \chi + y z'$  (sop)  $G = w' \chi (y + y')(z + z') + y z' (\chi + \chi') (w + w')$ = xywz + xywz'+ xywz'+ xyz' + xywz'+ xyw'z'+ x'yz'+ x'yw'z' = nyw'z + nyw'z' + ny w'z' + nywz' + xywz' + x'yw'z'

| (c) $T = f(a,b,c) = (a+b')(b'+c)(Pos)$                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------|

| Solve $T = (a+b')(b'+c)$                                                                                                           |

| = (a+b'+cc') (aa'+b'+c)                                                                                                            |

| = (a+b'+c)(a+b'+c')(a+b'+c)(a'+b'+c)<br>= (a+b'+c)(a+b'+c')(a'+b'+c)                                                               |

| (d) $J = f(A,B,C,D) = (A+B'+C)(A'+D)$ Pos.                                                                                         |

| J = (A + B' + C) (A' + D)<br>= (A + B' + C + DD') (A' + BB' + CC' + D)                                                             |

| = (A + B' + C + D) (A + B' + C + D') $(A' + B + C + D) (A' + B + C' + D) (A' + B' + C + D)$ $(A' + B' + C + D) (A' + B' + C' + D)$ |

|                                                                                                                                    |

- 2. Worite the canonical mintern and maxtern expressions for the following table up op a a b mSM Minteen Expression 0 0. 0 M= f(a,b,m,s) 000100 = Z(T,11,15) 00110 01000 = a'bms + ab'ms + abm 0101 01100 0 1 1 1 1 Maxteon Exp 1 0 0 0 0 M = f(a, b, m, s)10 1 0+0 + = T(0,1,2,3;4,5,6,8,9,10 10 1 1 7 1. .... IDO 110101110011119.2.3. antread de la condition

## Scanned with CamScanner<sup>46</sup>

$O_1 = f(c_1, c_2, c_3) = c_1' c_2' c_3 + c_1' c_2 c_3' + c_1' c_2 c_3' = \underbrace{\Xi(1, 2, 3)}_{= \underbrace{\Xi(1, 2, 3)}}$

$0_{2} = f(q_{1}, q_{2}, q_{3}) = c_{1}' c_{2}' c_{3}' + c_{2}' c_{3$

$$G_{22} = f(4, 52, 53) = 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 623 + 6$$

$w_1 = f(q_1, q_2, q_3) = q' q_2 q_3 + q_2 q_3 + q_3 q_$

$w_{22} f(q_1, q_2, q_3) = \frac{q_1 q_2 q_3}{5}$

# Scanned with CamScanner<sup>48</sup>

.b. J=f(ABCD)= (A+B+C+D) (A+B+C+D) (A+B'+C+D') (A'+B'+C+B) (A'+B+c'+D) (A'+B'+c'+D) (1,5,8,10,12,14) 5. White the Pos & sop equations for ASH' you the following Touth table. XYZ A A' Sop for A 000 0 0 001 1 A = = = (2, 4, 5) 0 010010-0 2 011 0 1 Sop to Al 3 100 1 0 101 | 1 0 | A' = E(0, 1, 3, 6, 7)110 Pos for A A = T(0, 1, 3, 6, 7)E. (2) L. 10, 14. Sop for A' -> A' = T (2,4,5) 1 Card States

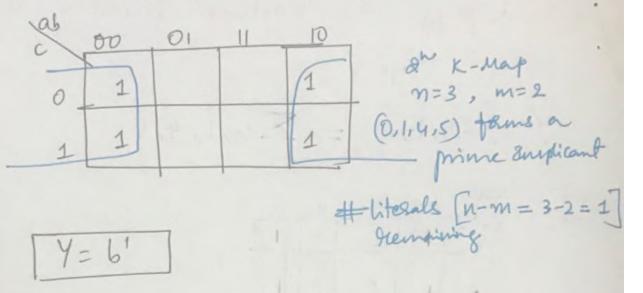

Pholdens on & Map. 1) Simplify the Boolean functing using 2-nap.  $Y = f(a, b, c) = \Sigma 0, 1, 4, 5$ Solv (ab 00 01 11 10 /= a'bc' + abc' - Two yroups of minteres Y= a'b' + ab one group of 4 mintesme. Y= 16 Y=abc+ abc + abc + abc = a'b' (c+c') + ab' (c+c') = ab + ab' = b (a+a') = b

## Scanned with CamScanner<sup>50</sup>

-X · X ·

3- variable K -Map showing Perime Implicant PI [0,1,4,5].

A set of 2 K-Map Squases all combined to grena Perime Inflicent, If n-variables of the equation being simplified by have a 2° permutations within the set and the siemening m-n Variables have the same value neith in the set. The resulting product teem has m-n literals.

In otherwarde 2° K-map Squares may be combined to form a yearp of mintelins containing m-n literale, where m supresents the no. of variables in the daginal equation.

Any single minterin of permitted youp of minterems is called an inplicant of an output function. A perime inplicant is a your of minterine that cannot be combined with any other minterns of yroups. Minteruns (0,1,4,5) are each Emplicants of Y. The prime implicants Consist of the 4 minterne yrouped to gether.  $G = f(x, y, z) = \sum (0, 2, 3, 7)$ , PE(Q,3) → X'Y Solw 24 00 01 EPI (0,2) > X'Z' 1975 -EPI (3,7) → YZ Expression G is loaded into the K-Map 3 groups of ninteens are found (0,2), (2,3) & (3,7)

## Scanned with CamScanner<sup>52</sup>

forma Perime tack of the 3 yroups insplicant. Perime Implicant (0,2) reduces to x'21 XY 111 (2,3) reduced to YZ. & (3,7) reduces to youps (0,2) and (3,7) both contain a minteren that is not in any other group. Mintern (0) is unique to PI (0,2) Mintern (7) is unique to PI (3,7). An Essential Prime amplicant [EPS] is a prime implicant in which one of more minteuns are unique i.e, it contains at least are minteren not contained in any other prime implicant. The simplified expression for & includes only the elsential fime implicants .. The non elsential perme implicant. (2,3) team is sudrundant because all of its mintelins are corrected by the

## Scanned with CamScanner <sup>53</sup>

Two essential prime amplicante.

The Simplified expression is Q= X'z'+ YZ.

Procedure for finding essential prime implicante ls this (a) find the prime Emplicants by finding all permitted maximum Sized youps of minteuns. 6) find essential prime emplicante by Edentifying those prime implicants that contain at least one mintern not found in any other prime Emplicant. 3  $D = f(\chi, \gamma, z) = \sum 0, 2, 4, 6.$ 2 10 D=z'

## Scanned with CamScanner<sup>54</sup>

$Q = f(a, b, c) = \sum_{i, 2, 3, b, 7}$ Solv C 00 2 1 1 4 3 1) 7 14 ITA Q= b+a'c - 2 perime Emplicants exist (1,3) 5 (2,3,67). Both ale eksential because each has a unique minterim 5) J= f(x,y,z) = 20,2,3,4,5,7 Sol 0 0 01 6 40 6 minterner containing 2 minterne exist. (02) > x'z' (3,7) -> YZ (0,4) -> y'z' (7,5) > XZ (415) - × × Y' (2,3) -> x'Y

The final simplified equation is not unique ie, more than one equally simplified result is possible. The product terms in the simplified heault must cover all of the minterine. - for ex, ne must pick a prime implicant (0,2) or (0,4) to cover the monterm(0) Two equally simplified equations are J= X'Z' + XY' + YZ which covers (0,2,3,4,57) J = y'z' + x'y + xzwhich covers (0,2,3,7,4,5) Simplify the following 4 - variable equations 6)  $K = f(w, x, y, z) = \sum_{i=1}^{i} 0, 1, 4, 5, 9, 11, 13, 15$ EPS (0,1,45) > WY Yz EPE (9,11,13,15) -> WZ 01 11 6 14 10 PI (1,5,9,13) -> ===

3 your variable Perime Emplicants are present \$0,1,4,53 \$9,11,13,1533 \$1,5,9,134 - 2 EPS are present 50, 1, 4, 5} \$9,11,13,152 Perine Emplicant \$1,5,9,132 is not essential because all of its minteress are contained in other 2 prime implicants. The final simplified equ is K= wy+wz  $L = f(a, b, c, d) = \sum 0, 2, 5, 7, 8, 10, 13, 15$ SOIN 10 81 12 00 L= bd+bd 00 51 1319 OI  $L = (b \oplus d)$ 15 11 TI 11 = 60d 14 10 10

$P=f(y_{1,5},t,u)=\sum(1,3,4,6,9,11,12,14)$ Jas tu 00 01 11 10 00 01 1 5 15 9 1 3 7 15 11 1 1 1 1 1 1 11 1 10 P= Su'+ du = Sou.  $D = f(w_1, x_1, y_2) = \sum (s, \tilde{\tau}, \tilde{s}, \tilde{q}, 13)$ Sol WX y2 00 01 11 10 y2 00 4 12 8 TF - EPE (8,9) > ywox OD 1 01 5 >PE(13,9) → Wyz 11 1012 6 14 EPE (SIT) > WWZ D SPE (SIB) > xy'z D= Whz twx y + xy'z D = WXZ + WXY + WYZ

## Scanned with CamScanner<sup>60</sup>

$T_{z}$ , f(w, x, y, z) = T(1,3,8,10,12,13,14,15)

(ty)

Simplify the following 5-variable expression using a K-Map. T= f(a,b,c,d,e) = E(0,2,8,10,16,18,24,26) w Jabe · 100 010. 011 DI . de 12 20 60 13 9 5 17 29 25 21 01 R M 23 31 3 19 27 14 10 22 8 30 26 10

conners in a 4-rainable map are logically adjacent. ent the S-variable map in the centre and wide the eight half over on top of the left , we can see that 4-Valiable maps aligned ventically. The square of one u-variable map is logically adjacent to the Square in the same relative position on

the four variable map.

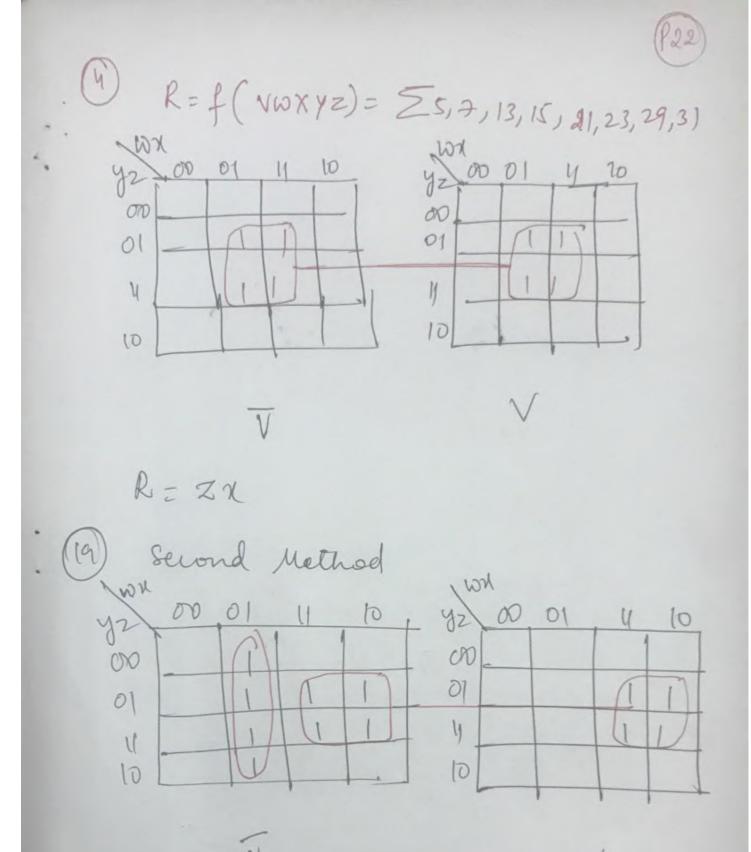

Minteum 303 is ventically aligned neith minteen 3163. III minteeing {2,18 3, {8,24} and \$10,26} are ventically aligned. Minterime located in all corners of each four variable map produces an EPI TECE. The centres of the 2, 4-vaenable X:Xmaps are also logically adjacent by the same reasoning.  $R = f(v, w, x, y, z) = \Sigma(S, T, 13, 1S, 21, 23, 29, 31)$ 100 101 111 000 011 op 9 01 11 51 19 28 31 1 27 11 26 14 18 10 R= XZ

W= f(a,b,c,d,e) = \(1,3,4,6,9,11,12,14,17,19) 20,22,25,27,28,30) ce si ak 110, 100 000 Lale h # lo 100 00 01 10 w=ee+ce 010, 10 100 000 (9) OD. · 01 :11 J= f(v, w, x, y, z)= > (4,5,6,7;9,11,13,15,25,27,29,81 YZ CPI OD S -K ist VIJX 10 J=WZ + VWX

## Scanned with CamScanner<sup>64</sup>

Y = a'(c'+b) + d a Write the truthstake and deign a circuit to generate op using k- Map for the problem Statement given \* op of a combinational cilicuit having 6M 4 Enpits and an op becomes logical I when two or mose enguls goto logical I. Solm abcd Y= 2 (3,5,6,7,9,10,11,12,13,14,15 00 00 abce D .00 U D 10 01 EPD Y= ab+cd+bc+bd+ad

obtain a minimal logical expression Jan 20 A for the given maxteren expression 4 Martis using K-Marp. F(a,b,c,d) = x (0,1,4,5,6,7,9,14)  $\Lambda(13,15)$ 00 01 12 13 (0) 15 MO 2.00 14 0 10 10 f(a,b,c,d) = (c+d') (a+b') (b'+c') (a+c) Use any method of minimization to Obtein PJs and Minimal expression. f'(a,b,c,d)=, Z(0,1,4,5,7,8,13,15)+Zd(2) 070000 530101 120001 770111 15-1111 43 PIOD choup o yeoup 4 youp 2 1 2 > 001D. General 3 8-1 1000

## Scanned with CamScanner<sup>66</sup>

Scanned with CamScanner<sup>67</sup>

Talked: Minter yours of the It convest the boolean function to (a) Y = f (a,b,c) = (a+b) (a+c) minteren. Canonical form. Y= f(a,b,c) = (a+b) (a+c) = aa tac + ba + bc = apac+ba+bc Y= f(a,b,c)= a(b+b)(c+c) + ac(b+b) +ba(c+c)+bc(a+a) = abo + abo + abo + abo + abo + abo +abet abe + abe + abe Y = abc + abc + abc + abc + abc. (b) P= f(a,b,c,d) = (a+b) (b+c) (c+a) mantesin Canonical form  $P = (a + b + c\bar{c})(b + c + a\bar{a}) + (a + b\bar{b} + \bar{c})$ = (a+b+c) (a+b+c) (a+b+c) (a+b+c) (a+b+c) (a+b+c) P= (a+b+c) (a+b+c) (a+b+c) (a+b+c) ]

#### Scanned with CamScanner<sup>68</sup>

Talles Mintern youngs of 4. a bed Group Minteam (0,1,4,5) 0-0-0 ac (0,4,1,5) 0-0-2 (5, 7, 13,15) -1-1 bd -1-1 (5,13,7,15) Table 3: Minteeur groups of (4). Perime Implicant Table PIS 0 1 4 5 7 8 13 15 X X X a'c' (0,1,4,5) XXXXXX bd (5,7,13,15) ] f(a,b,c,d) = a'c'+bd+b'c'd' (26) Find all the prime Emplicants of the function f (a, b, c, d) = TT (0,2,3,4,5,12,13) + TTd(8,10) · Sol D-> 0000 13-31101 270010 3-0011 Group3. 430100 5-20101 Groupo 12->1100 8#>1000 107->1010 - yeoup! yeoup2

# Scanned with CamScanner<sup>69</sup>

| step   | 1: As   | sange the creating # | maxteens<br>no. of 1's | in æder of |

|--------|---------|----------------------|------------------------|------------|

| 10     | poupo   | maxterim             | abed                   | 7          |

| t      | 0       | 0                    | 00000                  |            |

|        | 1       | 2                    | 0010-                  |            |

|        |         | . 4                  | 01000                  |            |

|        |         | 8-#                  | 1000                   |            |

|        | 2       | 3                    | 0011                   |            |

|        |         | 5                    | 0101                   | 14         |

|        |         | 10-1                 | 1010                   |            |

|        |         | 12                   | 1100-                  |            |

|        | 3       | 13                   | 1101/                  |            |

|        |         |                      | ( 12 mar and           | Lbt .      |

| Step 2 | : cyson | ming of n            | externs of             | order 2.   |

|        | ysoup ] | Maptern 1            | abed                   | e 7        |

|        | 0       | (02)~                | 00-0                   | 200        |

|        |         | (0,4)<br>(0,8+) V    | 0-00                   |            |

| -      | 1       | (2,3) X              | 001-                   |            |

|        |         | (2110*)~             | 2010                   |            |

|        |         | (415)                | 1010-                  | -          |

|        |         | (8#,10%)             | 10-0                   |            |

|        |         | (8#112)              | 1-00                   |            |

|        | 2       | (12;13)~             | 1101                   |            |

Masstelm yearping of order 4. step 3 : Maxteen abed yroup -0-0 -> btd\_ (0,2,8\*,10) (0, 4, 8\*,12) -- 00 -> c+d (0, 8\*, 2, 10") -0-0 -> btd (0,8t, 4,12) -- 00 -> ctd 1 (4,5,12,13) -10- b'+c Stepy! Prime Emplicant Table. Maxteen 0 2 3 4 5 12 13 8 10 x (x ghoup. bol XX ctd / x x k atto .1 XX XXXX Ttc Perine Emplicante ase (b+d), (c+d), (a+b+c) + (b+c) Simplified Boolean expression [M= (6+d) (a+6+i) (6+C) (cto) (atbtc) (bec)

# Scanned with CamScanner<sup>71</sup>

verification using K- Map. f(a, b, c, d) = TT(0, 2, 3, 4, 5, 12, 13)TId ( 8,10) 10 10 0 00 130 9 1 5 IS 11 2/ 7 14 10 M= (b+d) (b+c) (a+b+c)

(D) Using k-map determine the mininal (B) Sum af product expression and realize the simplified expression using NAND gales

M= f(w,x,y,z) = E(1,4.,5,6,11.,12,13,14,15)

M= wy'z + xz'+ wx+ wyz M = Z(wyfw'y') + x(zfw)

T ALL T

(28) Simplify the given boolean punction using. Quine - He cluskey Hethod. June verify the result using & map  $Y = f(a,b,c,d) = \Sigma(0,2,3,5,8,10,11)$ Solt (0 -> 0000 -> 40 33 0011 11 -> 1011 K 43. 53 0101-742 2- 0010 -4 10 ->1010 abid Minteren group 0000 2 0010 - 8 1000 0011 3 2 5 1017 10 010 3 | 11 1011 Take 1; Mintelen Georps of 1. Alanging minterins in increasing group 0 > 0 is yroup 2 > 2 ! group 1 > 1 1's youp3

# Scanned with CamScanner<sup>74</sup>

Table 2: Minterm exoups of two. abed Minterun group (0,2) 00-0 -000 (0,8) (2,3)/ 001 - 4 1 (2,10)/ -010 10-0+ (8,10) / (3,11) -0114 2 101-4 (10,11)/ Table 3: yroup of minteres of order 4. Minterim abed. group (0,2,8,10) -0-0 4bd'(0,8,2,10) -0-0 4bd'1 (2,3,10,11) -01-, 6'c (2;10,3,11) -01 -Talle 4! preation of PI lette PI Mintern 0 2 3 5 8 10 11 5'd' X.X (X) X (0,2,8,10). × (X) × (X) 6'c (2,3,10,11) date a abid

# Scanned with CamScanner<sup>75</sup>

its s is not mapped to any PIS it is added to the fim expression. ... Y= b'd'+ b'c + a'bc'd Verification noing k- Map. cd 100 01 11 10 PI3 5 (1) 18 01 6 PEI 4 5 . 16 14 10/1 PSZ 1 Y= b'c + b'd' + abe'd (29) find the minimal Sum for the incomplete Boolean function using QM method. & Prime Emplicant + Reduction f(a, b, c, d) = E. (3,4,5, 7,10,12,14,15) + 5 d (2).

P(B) Sol 330011 471000 111067 15>1111 5901011 2-30010 14-31110 geouple 123 1100 10>1010 - Group 1 group3 youp 2 Assange the mintering in increasing Step 1 : older of no. of 1's. abcd Mintelim group 0010 2\* 0100 -4 0011 2 3 5 0101 1100 3 14 4 15 1111 Step 2: Minterns of order 2.

# Scanned with CamScanner<sup>77</sup>

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                    | 1  | abcd    | Minterm ] | group 1 |

|-------------------------------------------------------------------------------------------------------------------------------------------|----|---------|-----------|---------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                     | Q  | 001 -×  | (2*,3)    | 11      |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                     | R  | 010 - × | (4,5)     | 0.1     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                     | 2  | -100×   |           |         |

| $\begin{array}{c} (5,7) & 01-1 \times \\ (12,14) & 11-0 \times \\ (10,14) & 1-10 \times \\ \hline 3 & (7,15) & -111 \times 1 \end{array}$ | T  | _010 ×  | (2010)    |         |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                     | 0  | 0-11×   | (3,7)     | 2       |

| (12,14) 11-0×<br>(10,14) 1-10×<br>3 (7,15) -111×1                                                                                         | V  | 01-1×   |           |         |

| 3 (7,15) -11 1×1                                                                                                                          | w  | 11-0×   |           |         |

| 3 (7,15) -11 1×1                                                                                                                          | X  | 1-10×   |           | 1       |

|                                                                                                                                           | Ty |         |           | 3       |

| (14,15) 111-×                                                                                                                             | Z  | 111-X   | (14,15)   |         |

Step 3: Grouping of minterens of order 4.

| 1 | p       | lint |    |     | 111 |       |

|---|---------|------|----|-----|-----|-------|

|   |         | 00   | SE | BIS | 1   |       |

| 7 | Jol     | Ko   |    |     |     |       |

|   |         |      |    |     |     |       |

|   | as into |      |    | 2.  |     | 1.8-1 |

(P19 Steph : Perine Emplicant table. Prov PI Q abc 3 H 5 24 X 10 14 15 12 XX R abc X S bod X T 6cd X X Vard X X v abd X X Wabo X X Xard X y bcd Zo abc X 4 X

Y= ADE + AB'C'DE + ADE + BCD TACD

f (ABLDE) = 5 m (213,4,6,11,12,14,17,18,) 20,22,25,28,30

EE + ACDE + AODE + BDE+-4 =

# Scanned with CamScanner<sup>80</sup>

f(ABCDE) 1) 19. to R

J= WZ + VWX

Scanned with CamScanner<sup>82</sup>

Obtain all the prime implicante of thegerer Boolean functions next Quine Mcchukery method. (1)  $f(abc) = \Xi m(0,2,3,4)$ a be op 01 1 10 0 10 1 1 10 1 10 Y= be 1 10 5 7 10 Y= be y= bc+ab PE (0,4) > be -> BPE PI (2,3) - ab -> EPI PE (0,2) -> QO -> PI abc Y group of 0'35 -> 000 -> 0. ~ 10000 Group of 1-1's -> 001 -> 1 001 0 010-72 2010 1 100742 young of 2-15 011-33 1 011 11 3 100 1 4 5 101 0 110 ->6 cproup of 3.-is 111 → 7 0 7/11/ 0 ) Grouping minterns according to no. of is group Minteur abe 000 0 010 2 100 AP 011 3 2

Table 2 : creation of minterns groups of 2

|   | yroup | Minter | abc |

|---|-------|--------|-----|

| - | 0     | 0,2    | 0-0 |

|   | U     | 0,4    | -00 |

|   | 1     | 2,3    | 01- |

|   |       |        |     |

Group of 0 - 1'S > 000 -> 0-Group of 1 - 1'S > 001 -> 2-100 -> 2-100 -> 4-100 -> 4-100 -> 4-100 -> 6-101 -> 5-

creation of monterns of 2. Fyronp | Mintern | abc Georging minterns according to

#### Scanned with CamScanner<sup>85</sup>

1910 Y2 a+5+0

| Solving Pos Desing OM technique.                                                                                                                                                                             |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ( Y = f(abcd) = TM(0,2,3,4,5,12,13) +TTd(8,10)                                                                                                                                                               |  |  |  |  |

| Solw<br>y = f(abcd) = TTM (0,2,3,4,5,8 <sup>+</sup> , 10 <sup>+</sup> , 12,13)<br>Mo M2 M3 Mu M5 M8 M10 M12 M13                                                                                              |  |  |  |  |

| Y = MO. M2 M3 M5 M8 M10 M12 M13                                                                                                                                                                              |  |  |  |  |

| Y = Mo M2 M3 M5 M8 M10 M12 M13                                                                                                                                                                               |  |  |  |  |

| $\overline{y} = \overline{\mathbf{R}}$ , $m_0 + m_2 + m_3 + m_5 + m_8 + m_{10} + m_{12} + m_{13}$                                                                                                            |  |  |  |  |

| let us apply QM technique to find the Prime                                                                                                                                                                  |  |  |  |  |

| Emplicante of $\overline{Y}$ .<br>Step1: tranging the minternes in order of no. of<br>is.<br>Group 1 $\rightarrow 0000 \doteq 0$<br>Group 1 $\rightarrow 0010 \doteq 2$<br>$\rightarrow 1000 \rightarrow 8A$ |  |  |  |  |

| $\begin{array}{rcl} qroup & 2 & \rightarrow & 0011 & \rightarrow 3 \\ & 0101 & \rightarrow 5 \\ & 1010 & \rightarrow 10^{*} \\ & 1100 & \rightarrow & 12 \end{array}$                                        |  |  |  |  |

| groups -> 1101 -> 13                                                                                                                                                                                         |  |  |  |  |

| Step 2<br>4704p of minteens in Ascending order<br>4704p minteen abcd<br>0 0 0000 ~<br>1 2 0010 ~<br>1 2 0010 ~<br>2 3 0011 ~<br>10 <sup>2</sup> 1000 ~<br>3 13 1101 ~                                        |  |  |  |  |

# Scanned with CamScanner<sup>87</sup>

steps: Group of minteenes of 2 P29) abed Mintern Group 00-0 V (0;2)(0,8\*)-000 V 001 - X (213) 1 +010+0 (2,10<sup>#</sup>) (8<sup>#</sup>,10<sup>#</sup>) 2020 V 1-00 X (ot,12) -101 X (5,13) 2 110-X (12,13) group of minteres of 4 stepy. 92000 Minlain abed 0 (0,2),8,15) -0-0  $(0,8^*)(2,18) - 0 - 0$ 1 Minlein Mash abed > b'd' btd (0 2 \$ 10) -0-0 PZ > ab' arbtc 001 -2,3) -> al'd' atcto 1-00  $\binom{8^{\#}, 12}{(5, 13)}$ -> bc'd\* btctd -101 -> abe' appre 110-(12,13) (btd) (atbtd) (atctd) (tot ctd) (atbtc)

#### Scanned with CamScanner<sup>88</sup>

$Y = f(abcd) = \pi (0, 2, 3, 4, 5, 12, 13) + dc (8, 10)$ [Y = (a+b+z) (b+d) (c+d) (b+c)

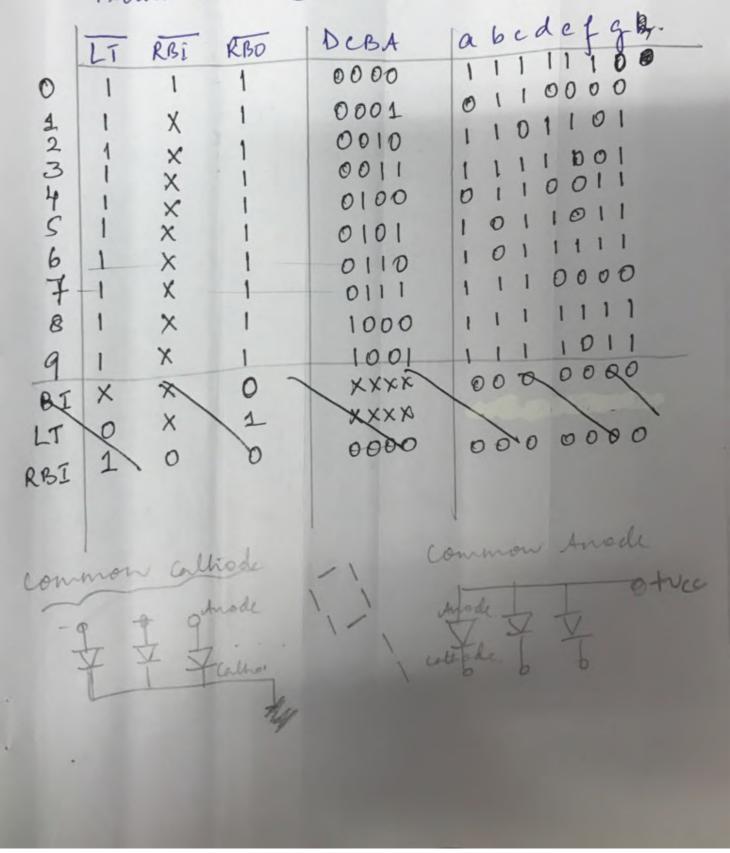

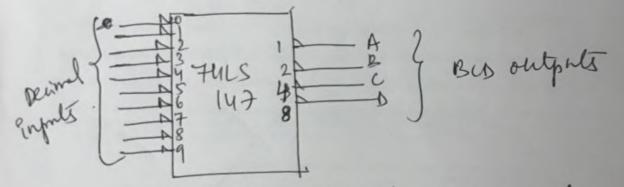

DM SAI MODULE 2: ANALYSIS AND DESIGN OF COMBINATIONAL LOGIC - youreal approach to combinational logic design Decoders (a) BCD Decoders Eucodeus Digital Unthiplexeus (a) Using Multiplexens as Boolean function generatore. "Address and Substantons (a) cascading full adders (b) Look ahead carry Snavy comparators. ECE

general approach to combinational dogie Deign. The synthesis of combinational logic starts with a problem statement and progresses through a serier of steps, terminating in the final circunit design . - The combinational logic design steps are as follows. as follows. Step 1 : Develop a statement descenting the problem to be solved. Step 2: Based on the firsten statement, Construct a territe table that clearly establishes the relation you the Eught and output variables Step 3: Use K-Maps of QM Techniques to simplify the functions in desiring the output equations. This may require that the output equations be expressed as either SOP of Pos. The best solution will require the fewest gates and gate inputs. Stept: Arrange the Simplified equations to suit the logic frimitive lype to be need in realizing the circunit. (Using NANDS, NORS of tND-OR dogic required) Steps: Draw the final logic diagram. Steph: Document the design by identifying variables names that indicate assession devels, if possible provide Truth table.

# Scanned with CamScanner<sup>91</sup>

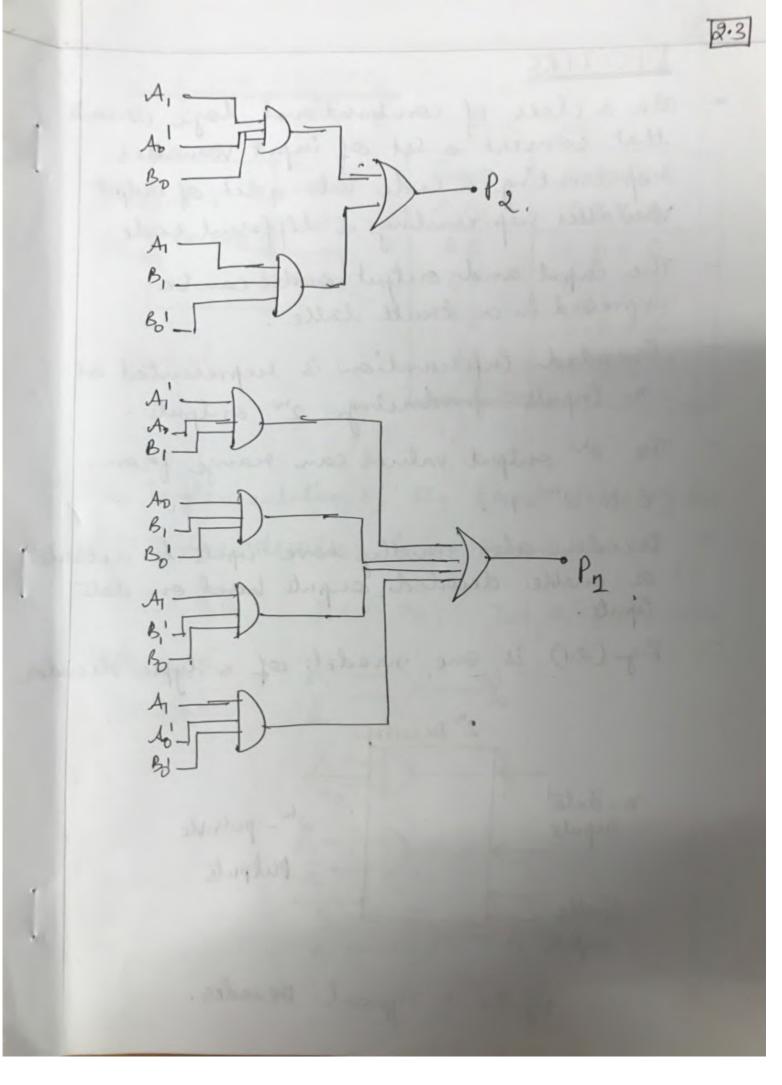

Example: Design a combinational circuit that will multiply 2, 2-bit binary values Solv O det the inputs be A (A, Ao) & B(B,, Bo), and the output be P(P3,P2,P,,P0). The four output variables are necessary because the maximum product of two, 2-bit values reques 4 bits. Ledelch valiable be active high D Construct the Truth table (Next page) 3 The individual simplified equations are . A Ao  $P_3 = A_1 A_0 B_1 B_0.$ Bo  $P_2 = A_1 A_0' B_0 + A_1 B_1 B_0'$ Bit Byto X  $P_1 = A_1 A_0 B_1 + A_0 B_1 B_0 + A_1 B_1 B_0 + A_1 A_0 B_0$ Po = Aobo. ABJER ADBO BA

Tenth table P3P2P, Po 0 110 D Logic Bingham for 2x2-bit Unltiplier to B lg. Bo Bo Po.

# Scanned with CamScanner<sup>93</sup>

# Scanned with CamScanner<sup>94</sup>

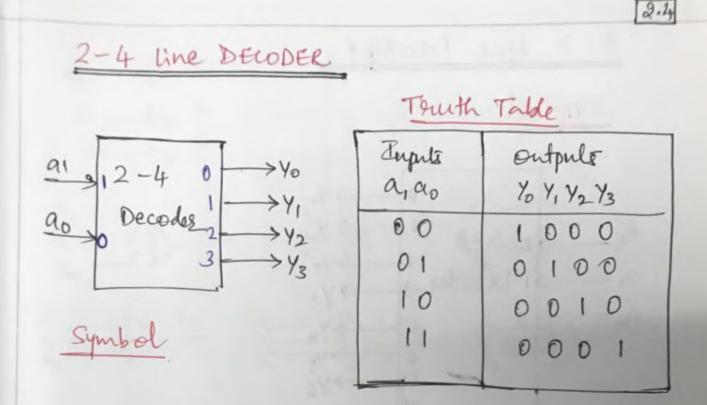

# DECODERS.

are a clace of combinational logic circuits that convert a set of input variables representing a code into a set of output vairables représenting à différent code. The Engent and output codes can be expressed in a touth table . Encoded Enformation is represented as n inputs producing 2ª outpute. The 2 output values can range from 0 6 2 -1 Decoders also venally have inputs to actuate or enable decoded oupsts based on data impute. typute. Fig (2.1) is one model of a typic decoder 2 Decodes n-data Enputs 2 - possible Outpute Enable infinte fig 2.1 : Typical Decodes.

# Scanned with CamScanner<sup>95</sup>

- The implementation of the territe table of the 2 to 4 line decoder is as shown.

- $Y_{0} = \overline{a_{1}}\overline{a_{0}} , Y_{1} = \overline{a_{1}}a_{0} , Y_{2} = a_{1}\overline{a_{0}} , Y_{3} = a_{1}a_{0} .$   $a_{1} \longrightarrow \overline{a_{1}} \qquad \overline{a_{1}} \longrightarrow Y_{0} \qquad \overline{a_{0}} \longrightarrow Y_{1} \qquad A_{1} \longrightarrow Y_{1} \qquad A_{1} \longrightarrow Y_{2} \qquad A_{1} \longrightarrow Y_{2} \qquad A_{1} \longrightarrow Y_{2} \qquad A_{1} \longrightarrow Y_{2} \qquad A_{1} \longrightarrow Y_{3} \qquad A_{2} \longrightarrow Y_{3} \qquad A_{3} \longrightarrow Y_{3} \longrightarrow Y$

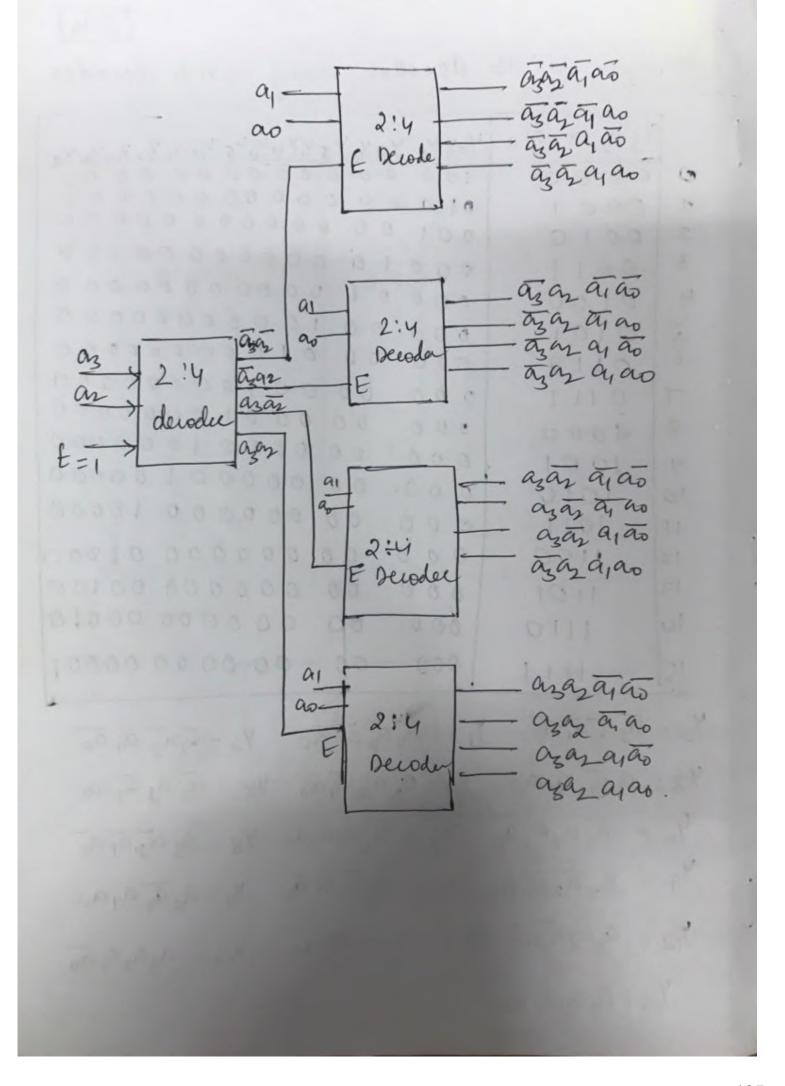

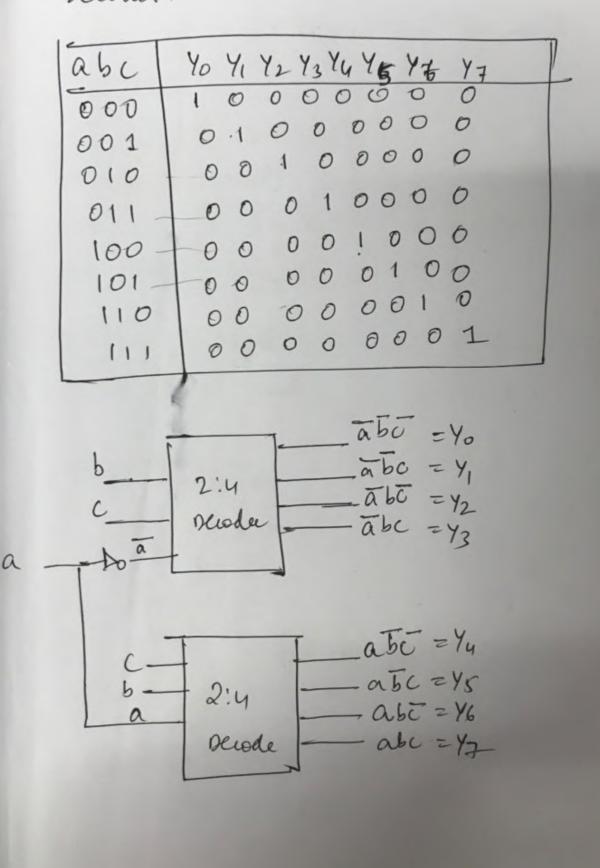

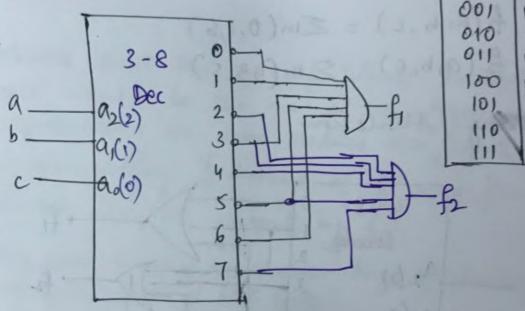

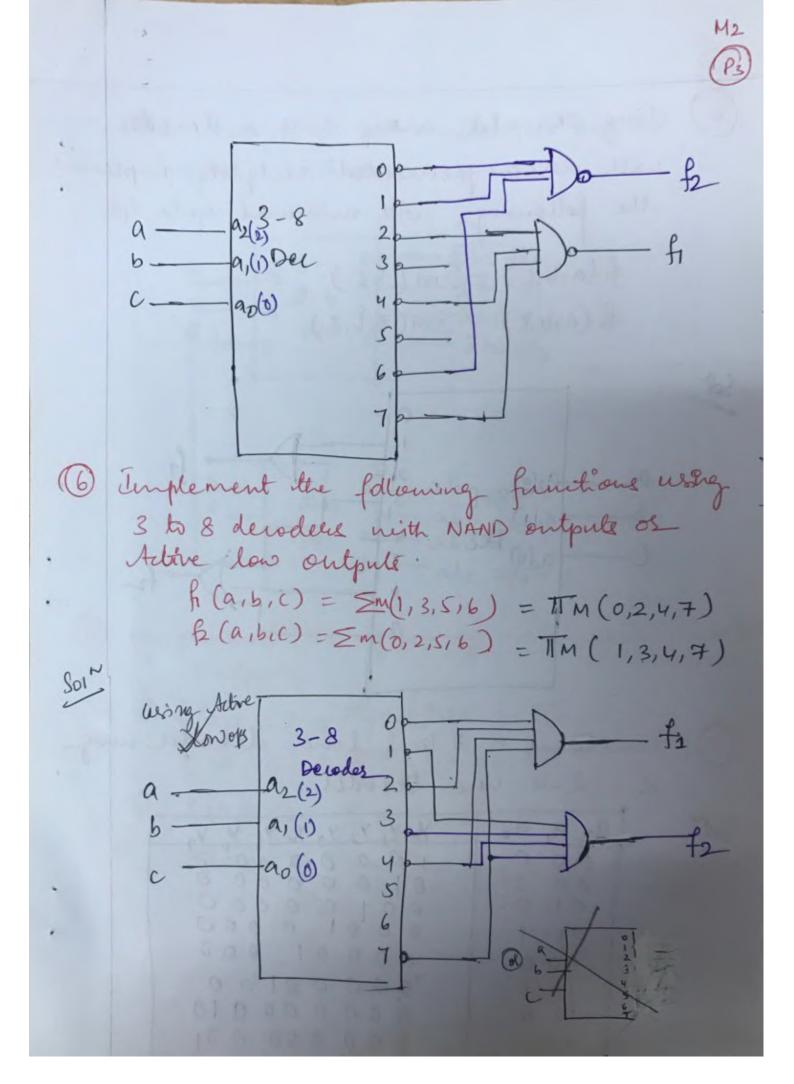

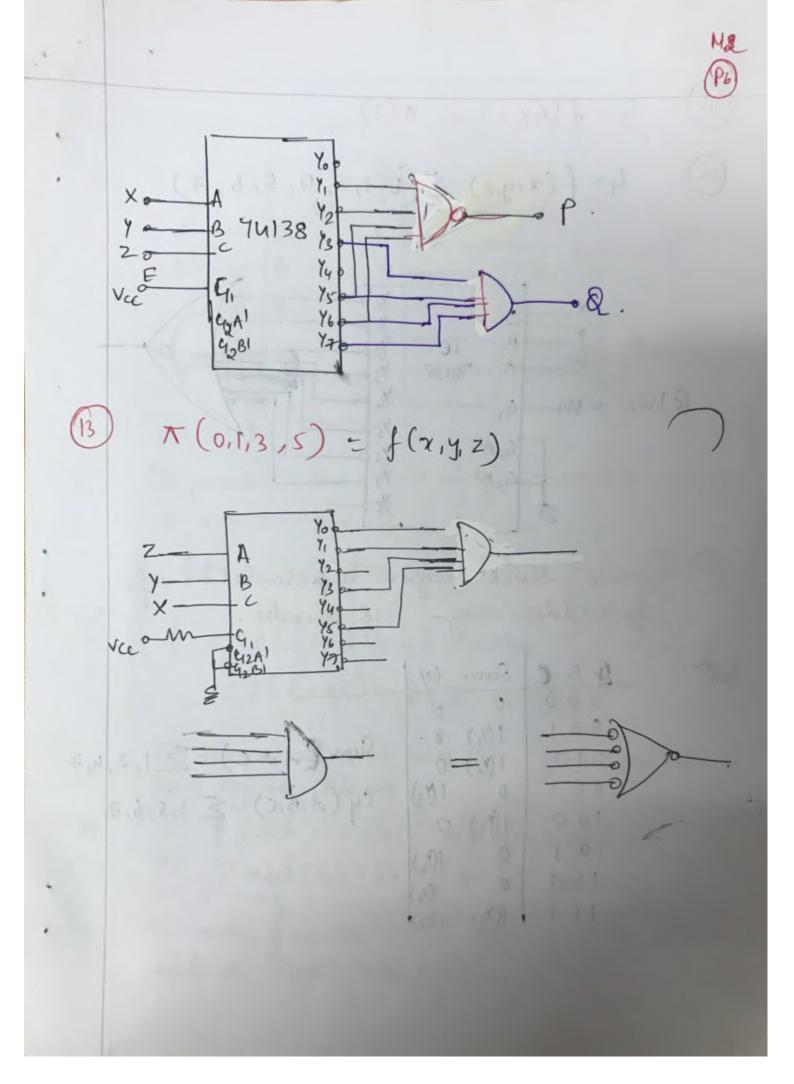

12.5 az - Jo az ai <u>boa</u> ac ba 10  $a_1$   $b_1$   $a_2$   $b_1$   $a_2$   $b_1$   $a_1$   $b_2$  $a_1 =$   $Y_3 = a_1 =$   $Y_4 = a_1 =$  $a_1 = \frac{y_6}{a_1} = \frac{y_7}{y_6}$ Logic Design using Decoders. Each output of the decodes generates a minteren A 2-4 deroder generates 4 minteren using 2 variables and a 3 to 8 decoder generales minterins with 3 Variables. Thus a not 2" line deroder is very converient to generale n variable minterne and realize a SOP expression.

# Scanned with CamScanner<sup>98</sup>

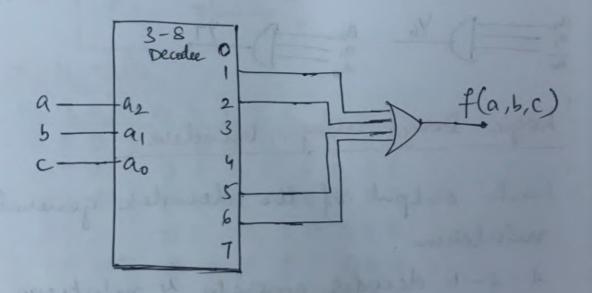

consider the implementation of the following function.  $f(a,b,c) = \overline{abc} + \overline{abc} + \overline{abc} + \overline{abc} + \overline{abc}$ = Im (1,2,5,6)

This can be implemented noing a 3tos line decoder is asshonen.

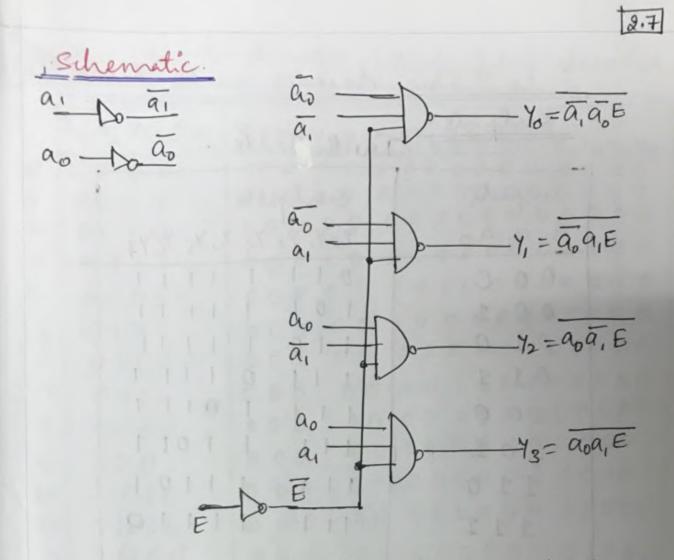

# DECODERS WITH ENABLE ENPOT.

In general, in decodeurs one of the op's always 1 in the uncomplemented op version & one of the ops is always 0 in the complemented Verision.

- There are several applications where we would want all the outputs to be at 0 & 1 deepertively.

- This can be achieved by including an enable input to the decoder.

- The touth latte, symbol and schematic of 2 to 4 line decoder with an enable type and uncomplemented op is as showen,

| 2 to 4 l | ine Decod | er neith                               | Erable input.       |

|----------|-----------|----------------------------------------|---------------------|

|          | (ACTIVE   | E HIGH)                                | them and the second |

| symbol   |           | AND IN THE REAL PROPERTY AND INCOMENTS | with Talle          |

| a There is a second sec | Cuputs | ontputs     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|

| a. 12 to 4 0 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Earao  | Yo Y, Y2 Y3 |

| ao o Decoda Yi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0 X p  | 0000        |

| E Y2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 100    | 1000        |

| pppixx 5 yz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 101    | 0100        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 110    | 0010        |